Jeg har i de tidligere blog posts lavet kredslæb der kan styre DCC preamble, data byte start bit, command end bit og naturligvis selve DCC signalet. Så det er nok på tide at få det sat sammen så jeg kan begynde at se et signal der kunne sendes til boosteren.

Jeg har endnu ikke låst mig fast på kredsløbet for shift-registrerne hvor kommandoen læses fra - så indtil videre fodrer jeg bare "1" eller "0" ind istedet for output fra shiftregistret.

Logikken er forholdsvis simpel:

- Hvis vi er i preamble skal signalet være 1, ellers:

- Hvis vi er i "command end bit" skal signalet være 1, ellers:

- Hvis vi er i "data byte start bit" skal signalet være 0, ellers:

- signalet skal læses fra shift registrerne.

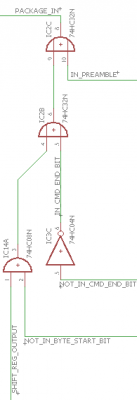

Kredsløbet der bygger dette op kan se ud som følger:

så det er forholdsvist enkelt. Der er desværre introduceret en AND gate, så det burde betyde endnu en IC - som der ellers allerede er nok af.

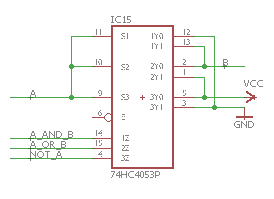

Men jeg har en 74HC4053 i kredsløbet hvor jeg genererer klokken hvor kun 1 ud af de 3 gates er brugt. Hvis jeg ikke har mere der skal multiplexes, så kan de sidste to gates bruges som AND, OR, eller inverter gates - alt efter hvad jeg lige får brug for. Dette kan laves som illustreret i dette kredsløb:

I dette tilfælde har jeg stadig OR gates tilgængeligt, så jeg behøver kun at "låne" en AND gate - så eksemplet der er forbundet til gate 1 i dette diagram. Bemærk at jeg indtil videre beholder AND gaten i mine diagrammer - det er lettere at arbejde med. Det er nok først når der loddes jeg opdaterer diagrammet til at bruge gates fra 74HC4053'eren. Og hvem ved, måske jeg ender med at skulle bruge nok AND gates til at jeg lige så godt kan bruge en 74HC08 som i diagrammerne.

Signalet ser nu sådan her ud når alle databits sættes til 1:

selve DCC signalet der skal gå til boosteren er øverst, Derefter signalet der styrer "end of command", og nederst "in preamble". Alt ser ud som det skal. Jeg forsøgte mig også med 0 på alle databits, og igen så det ud som jeg forventede.

Det næste project er at få helt styr på enable/disable så signalet ikke som nu kan blive enabled midt i en preamble. Jeg har allerede noget kørende, men jeg tror jeg ændrer den måde shIft registerne er styret på - så kan jeg spare én IC - så der er lidt mindre at lodde. Mere om det senere.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Mandag d. 30/1/2017 - 21:02

Mandag d. 30/1/2017 - 21:02

0 kan lide

0 kan lide

HEDO

Pension, tidl. DSB IT

Indlæg: 190

Hej

Prøv at se på Litra.dk hjemmeside under booster og DCC. Der er også diagram.

Mvh. Henrik D.

Henrik D.

Modeljernbane gennem 50 år. Kører nu 2 skinne digital system med dansk landskab.

Formand for Køge Modeljernbane Klub KMK. Medredaktør af Mosebanens Klubnyt.

lmoelleb

Doorwerth Netherlands

Indlæg: 91

Ja, det ser rimeligt nyttigt ud når jeg kommer til boosterne - jeg har set ideen med 12v pærer før - så evt går jeg i den retning. Vi får se, der er et godt stykke vej endnu....

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Skott

Ingeniør

Indlæg: 1.954

Hvis du vil undgå din AND-gate, Så kan du erstatte med en OR-gate og så invertere begge indgange , altså sætte en inverter på hver ingang. Til sidst sætter du så også en inverter på udgangen af OR-gateb. Hermed sparer du en kreds

Med venlig hilsen

Skott

lmoelleb

Doorwerth Netherlands

Indlæg: 91

Jeg er klar over det, men der er også ved at være udsolgt af de 4 or gates jeg har til rådighed uden at smide endnu en IC ind. Så vi får se hvad der er bedst når jeg har styr på hvilke gates jeg skal bruge i hele kredsløbet.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Skott

Ingeniør

Indlæg: 1.954

Ok

Med venlig hilsen

Skott