Efter at have genereret et signal der kan indsætte DCC data byte start bits i sidste indlæg er turen kommet til at få afsluttet kommandoen.

Dette gøres ved at sende 1 efter den sidste byte. Jeg regnede egentlig med at det ville være en større udfordring at få rigtig - man kan jo let løbe ind i noget +/- 1 hvor den får bitten sat for sent eller for tidligt. Men man har jo også lov at være heldig en gang imellem, og det blev løst med en enkelt IC - igen en counter, men denne gang en 74HC193N. Den største forskel på denne counter og de 74HC163N jeg brugte tidligere er at 193'eren kan tælle både op og ned. Derudover er reset og load asynkront (nå ja, der er også lige den detalje at master reset er aktivt når den er høj og ikke lavt... det kostede et par minutter).

Jeg aktiverer chippens parallel load mens der er preamble. Derefter tæller jeg ned hver gang der er en ny start byte. Jeg havde ikke liiige læst datasheet korrekt da jeg lavede kredsløbet. TCD - terminal count down der går højt når man er kommet til 0 bliver først aktiv når count down pulsen går lav. Av. Det betød at jeg smed packet end bitten ind efter en byte start bit istedet for at erstatte den. Efter lidt grublen indså jeg heldigvis at jeg bare kan bruge en inverterer IN_BYTE_START_BIT - som jeg allerede har - til at aktivere count down. Det betyder at registret er lidt "foran" når det tæller ned - så det kommer til 0 når den sidste byte begynder, og signalerer "overflow" når den diste byte slutter. Men det betyder blot at vi kører data bytes med 0 index - og som programmør er det jo nærmest at foretrække.

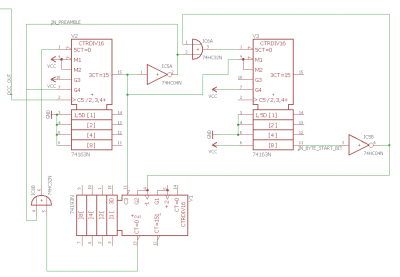

Diagrammet ser nu sådan her ud:

Den nye counter er nederst. Der er også kommet en ekstra inverter (not gate) efter genereringen af byte start bits - den var der nu også i sidste post, men jeg fik åbenbart ikke gemt den rigtige version.

I analyzeren ser det sådan her ud når den er "hard wired" til 3 bytes kommandoer:

DCC signalet skal stadig genereres ud fra dette. Hvis "End of command" er lav eller "In preamble" er højt skal DCC signalet sende 1. Er dette ikke tilfældet men In byte start bit er høj skal der sendes 0. Ellers skal output fra shift registrerne sendes. Det er let nok at gøre - men jeg venter nok med det indtil jeg har lidt mere styr på shift registrerne. Når de er på plads ved jeg nok lidt mere om jeg har introduceret AND gates eller lignende der kan hjælpe.

Min breadboard er også ved at have opslugt alle mine ledninger, så det ville være rart hvis noget af det snart kunne flyttes til et protoboard. Så det kan godt være jeg ikke fortsætter før klock generatoren er flyttet over... vi får se.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Mandag d. 23/1/2017 - 22:53

Mandag d. 23/1/2017 - 22:53

1 kan lide

1 kan lide