If sidste afsnit af mit bindegale projekt med at generere DCC kommandoer med simple off-the-shelves komponenter fik jeg lavet et simpelt kredsløb der kan styre længden af det DCC preamble der starter en ny kommando. Preamblet skal bestå af 1 der bliver sendt 14 eller flere gange.

Jeg finder DCC specifikationen forholdsvis rodet med Packet Start Bit, Address Data Byte, Data Byte Start Bit, Data Byte, og Packet End Bit.

Egentlig skal man bare sende en 0 bit efterfulgt af en data byte indtil der ikke er flere bytes at sende - så sender man en 1 bit (der kan være starten på næste kommando's preamble.

Så jeg har altså brug for noget der kan holde styr på hvornår preamble er slut, og derefter angive hver 9 bit indtil næste kommando.

Det er forholdsvist trivielt med endnu en 74163 counter - den samme jeg brugte til at styre preamblet.

Her bruger jeg bit 3 ( det går høj når den har sendt 8 bits. Når den går høj resetter jeg counteren på næste clock så den går tilbage på 0, og bit 3 går lav igen indtil de næste 8 bits er sendt.

det går høj når den har sendt 8 bits. Når den går høj resetter jeg counteren på næste clock så den går tilbage på 0, og bit 3 går lav igen indtil de næste 8 bits er sendt.

Som beskrevet her vil det - som ønsket - generere et signal der angiver hver 9 bit. Men det skal også startes så den første bit after preamblet bliver markeret. En løsning ville være at resette counteren i preamblet og så bruge en OR på output bit 0,1,og 2, og 3. Når de alle er lave er det den første bit efter preamblet og derefter hver 9. bit.

Jeg har istedet valgt at loade counteren med værdien 8 når preamble bitten er høj. Så starter output bit 3 høj som ønsket og counteren resetter sig selv. Desværre er der stadig brug for en enkel OR gate. Uden den bliver counteren sat til LOAD i starten af preamblet. Det får så RESET til at sætte counteren til 0 (selv om LOAD stadig er sat), hvorefter LOAD igen sætter den til 8, og så fortsætter det med at gå høj og lav igennem preamblet. Det kan jeg et godt leve med hvis jeg styrer længden af preamblet - vi får se om jeg kan smide OR gaten væk når (hvis) jeg får styr på resten af kredsløbet.

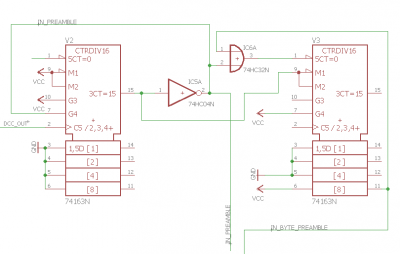

Sammen med preamble kredsløbet fra sidste blog post ser det nu sådan her ud:

Jeg fik kaldt byte start bit for byte preamble i kredslæbet, det er nok noget jeg retter senere.

Preamble styres af chippen til venstre, byte start bits af chippen til højre. Pin 9 der styres af preamblet er LOAD (aktivt lavt), og som nævnt sikrer OR gaten at RESET (pin 1) ikke går lavt mens preamblet er aktivt.

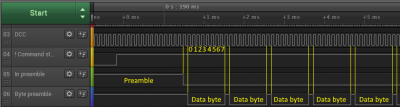

Det giver følgende output på logic analyzeren, så det ser ud til at det stadig er brugbart:

Så planen er at hvis preamble er højt så sendes 1. Hvis preamble er lavt men byte preamble (altså byte start bit) er høj, så sendes 0. Ellers sendes kommandoen fra shift registre.

Den større udfordring er nu at få stoppet efter den sidste byte er sendt - og endten generere en stop bit på en eller anden måde, eller få started det næste preamble lige efter byten er sendt - så den første 1 bit i preamblet kommer til at fungere som stop bit. Det er nok den største udfordring jeg har nu. Heldigvis er det kon 3-6 bytes længde der er nødvendigt, så man kan både bruge shiftregistre og 4 bit countere til at styre det - vi må se hvad jeg finder ud af.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Lørdag d. 21/1/2017 - 18:02

Lørdag d. 21/1/2017 - 18:02

0 kan lide

0 kan lide