Når kommandoen skal udlæses fra shiftregistrerne er det lidt kompliceret da kommandoerne vil være mellem 3 og 6 bytes.

Udfordringen er at en 3 byte kommando vil blive indlæst i de "bagerste" 3 shift registre, mens de tre "foreste" vil have tilfældige data fra den tidligere kommando.

Det letteste ville være at få computeren (raspberry pi eller hvad det nu bliver) til at generere signalet "baglæns", så kan det bare køres ud i modsat rækkefølge det kom ind med. Men nu har jeg jo sat mig for at undgå at computeren skal lave den slags beregninger (ellers havde jeg været færdig for længst).

Så enten skal input styres ind i de rigtige registre (så input ikke bare er forbundet i serie) eller også må jeg sikre mig at de ikke altid udlæses fra "enden" af de 6 registre. Jeg har valgt den sidste løsning.

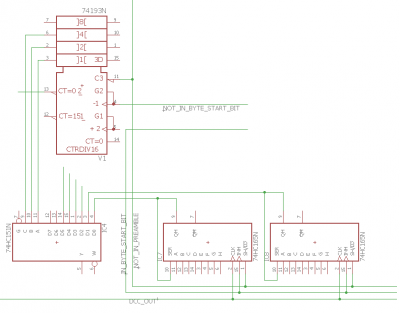

Min første plan var at bruge en 8 line multiplexer (74HC151) med addresse pins forbundet til output af den counter jeg bruger til at finde slutningen af kommandoen. Den tæller ned til 0, så jeg kan "løbe" mellem shiftregistrerne. De skal så ikke forbindes i serie men loope internt. Det ville være noget i denne stil:

Jeg har kun inkluderet 2 shiftregistrer på tegningen. Jeg ville mene det skulle virke som det er... men der var et problem... Mine 74HC151 chips vra stadig på vej fra Kina. Og mens jeg ventede fik jeg nye planer.

Ud over at "samle signalet" (mere om det senere) er der stadig én funktion jeg ønsker at tilføje på output siden: enable/disable. Jeg vil lave det sådan at computeren kan "slukke" ved at sende en kommando der er for kort - for eksempel ved at sende en enkelt byte. Det kunne laves ved at se på om bit 1 eller 2 er sat når man tæller bytes. Men så skulle jeg bruge en latch eller flip flop til at "huske" dette mens kommandoen sendes. Altså ville jeg få brug for mindst 1 IC mere (og jeg ville bruge endnu en OR gate).

Jeg fik så en ny idé. Jeg havde allerede fået en dual 4 bit multiplexer (74HC153) leveret. Den kan multiplexe 2x4 linier ned til 2 linier - men der kan kun sættes én addresse. Så har man valgt linie 3 i blok 1, så får man også linie 3 i blok 2.

Planen er at der vil være en counter der angiver antal bytes modtaget fra computeren (counteren vil tælle bits, men smider man de sidste 3 bits væk har man antallet af bytes). Det vil alså give følgende kombinationer:

| Antal bytes | Antal bytes i binær | Shift register output |

| 0 | 0000 | Disable |

| 1 | 0001 | Disable |

| 2 | 0010 | Disable |

| 3 | 0011 | 3 |

| 4 | 0100 | 2 |

| 5 | 0101 | 1 |

| 6 | 0110 | 0 |

| 7 | 0111 | Disable |

| 8 | 1000 | Disable |

De to sidste bits (markeret med fed) kan bruges som input i 74HC153 multiplexeren, der så kan vælge input shift register 0 - 3. Roder man lidt med bittene kan man også udlede hvornår signalet skal disables. Der skal altid disables hvis bit 4 er sat - det har 74HC153 heldigvis et ekstra ben der let håndterer - sættes det til højt (altså direkt til bit 4) vil enable altid være lav. Jeg burde også kigge på ben 5, ... men det såringer jeg over - sender man for mange bytes for man et tilfældigt resultat. Det kan stoppes i det kredsløb der modtager signalet fra computeren, men det ved jeg ikke om jeg gider bruge kræfter på. Så jeg kan bare se på pin 3 for at se om enable skal være højt for et givet input.

| Bits | Gyldig kommando længde | Ugylding kommando længde | Regel for enable |

| 00 | 4 | 0 | bit 3 høj |

| 01 | 5 | 1 | bit 3 høj |

| 10 | 6 | 2 | bit 3 høj |

| 11 | 3 | 7 | bit 3 lav |

Så jeg kan bare smide bit 3 ind på de første 3 linier i blok 2 af multiplexeren, og inverteret bit 3 ind på den sidste linie. Så vælger multiplexeren enable/disable sammen med valget af shift register. Jeg skal dog sikre mig at det valgte shiftregister fastholdes igennem hele kommandoen - og ikke skifter halvvejs når computeren sender en ny kommando. Dette gør jeg med en 4 bit latch (74HC75) der fastholder antal bytes i den kommando der sendes.

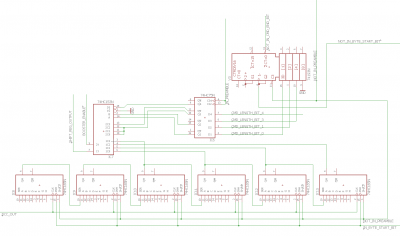

Det giver følgende kredsløb:

CMD_LENGTH_BIT forbindelserne er kun input (til counter og latch), de bliver forbundet med en counter på input siden.

En ulempe med dette kredløb er at jeg lader shift registre og counter latch loade parallelt under hele preamble. Det betyder ikke noget for kommando output, men det kan gå galt med enable/disable. Hvis boosteren er disabled og computeren sender en ny kommando halvvejs inde i preambled så enabler jeg kredsløbet selv om det kun kan nå at sende en halv preamble. Det ville være bedre hvis jeg kun loadede counter latch og shift registrer lige når preamblet starter. Det vil jeg tænke lidt nærmere over. Nu er min 74HC151 ankommet, så hvis jeg kan lave en pulse detektor og enable/disable med en enkelt IC, så er det måske værd at forsøge.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.

Lørdag d. 28/1/2017 - 17:10

Lørdag d. 28/1/2017 - 17:10

1 kan lide

1 kan lide

GustavSVJ

Studerende

Indlæg: 15

Hej Lars,

Jeg er dybt imponeret over dit projekt og har med stor fornøjelse læst med

Jeg har personligt forsøgt mig med en Arduino og har da også fået det til at virke... Men din tilgang til problemet er, omend besværlig, super lærerig og yderst interresant at følge!

Mvh,

Gustav

lmoelleb

Doorwerth Netherlands

Indlæg: 91

Hej Gustav,

Jeg finder det meget afslappende at sidde og rode med det her projekt. Der er både tid ved computeren hvor det hele udtænkes, og tid hvor man sidder og fedter med strøm. Det passer mig perfekt.

Jeg skal bare passe på jeg ikke går for langt. Jeg kom lige til at tænke "man kunne også have en kø af kommandoer som den cykler igennem så min Raspberry PI ikke skal gentage kommandoerne hele tiden"... men jeg må hellere lade være med den slags skøre ting - det er skørt nok som det er.

mvh

Lars M

Er så småt ved at begynde at pille i skala n, epoke III, DB.